Questões de Engenharia Elétrica

Lista completa de Questões de Engenharia Elétrica para resolução totalmente grátis. Selecione os assuntos no filtro de questões e comece a resolver exercícios.

Para um sinal com pico de tensão de 100 mV (sem ruído) recebido, o valor root mean square (RMS) máximo do ruído, correspondente a uma probabilidade de erro de 108 erros/bit, considerando 100,65 = 4,467, será inferior a 25 mV RMS.

- C. Certo

- E. Errado

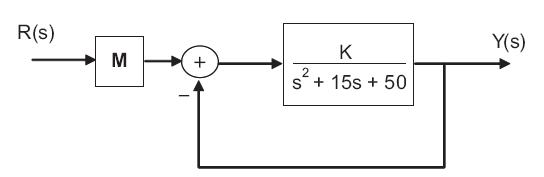

A figura acima apresenta o diagrama em blocos de um sistema de controle em malha fechada. Para que no domínio do tempo a saída y(t) siga a entrada de referência r(t), do tipo degrau, com erro de estado estacionário NULO, a expressão do ganho M será

- A.

K/50

- B.

K/K +50

- C.

1/K

- D.

1/K +50

- E.

K +50/K

Engenharia Elétrica - Eletrônica Analógica - Centro de Seleção e de Promoção de Eventos UnB (CESPE) - 2010

O diagrama de bloco mostrado na figura acima ilustra a entrada X(s) e a saída Y(s) de um sistema dinâmico, cuja função de transferência é H(s). Considere que, à entrada do sistema, seja aplicado um impulso unitário X(s) = 1, sendo então observada a resposta Y(s) resultante. Considere, ainda, que a transformada de Laplace Y(s) do sinal observado nos terminais de saída possua zeros z1 = 2 e z2 = 1, e polos p1 = 0, p2 = 2, p3 = 2 e p4 = 5, e que Y(s) represente uma tensão e Y(2) = 0,5 V. Com base nessas considerações, julgue os seguintes itens.

Em regime permanente, a amplitude do sinal de saída é dada por

- C. Certo

- E. Errado

Engenharia Elétrica - Eletrônica digital - Centro de Seleção e de Promoção de Eventos UnB (CESPE) - 2010

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue os itens que se seguem.

- C. Certo

- E. Errado

Engenharia Elétrica - Máquinas Elétricas - Centro de Seleção e de Promoção de Eventos UnB (CESPE) - 2010

A respeito do acionamento elétrico e da proteção de motores, julgue os itens seguintes.

O termo inversor de frequência corresponde à tradução do termo inglês relacionada ao equipamento soft starter, o qual é utilizado para controlar a velocidade do motor de indução, tanto durante a partida quanto em regime permanente, sem afetar o valor do conjugado de partida.

- C. Certo

- E. Errado

A mensagem binária 10100111, representada pelos níveis de sinal mostrados na figura A acima, será transmitida. Para essa finalidade, são projetados circuitos digitais para separar os bits em grupos de dois, na medida em que eles chegam em série do computador, sendo alocado, para cada par, um entre quatro níveis de tensão possíveis. Assim, aos pares binários (00), (01), (10) e (11) são atribuídas as tensões 0 V, 1 V, 2 V e 3 V, respectivamente. Dessa forma, para enviar a mensagem binária 10100111, o sistema quaternário desenvolvido deve transmitir 2 V, 2 V, 1 V e 3 V, conforme ilustrado na figura B acima. Com base nessas informações, julgue os itens seguintes.

A taxa de transferência e a taxa de baud da transmissão quaternária correspondem, respectivamente, ao dobro da taxa de transferência e ao dobro da taxa de baud da transmissão binária.

- C. Certo

- E. Errado

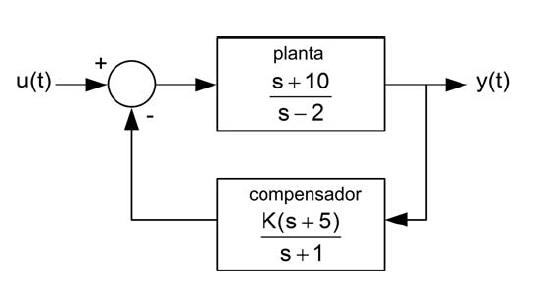

Coonsidere a figura e os dados abaixo para responder às questões de nos 41 e 42

A figura acima ilustra um sistema de controle em que uma planta com comportamento instável é estabilizada por meio de um compensador. Os modelos matemáticos da planta e do compensador encontram-se na figura. O compensador apresenta um ganho positivo K que deverá ser ajustado.

Verifica-se que para um determinado valor de K, o sistema em malha fechada apresenta um polo localizado em s = −8 . Este valor é

- A.

35/3

- B.

40/3

- C.

45/6

- D.

55/6

- E.

65/9

Engenharia Elétrica - Eletrônica Analógica - Centro de Seleção e de Promoção de Eventos UnB (CESPE) - 2010

O circuito acima representa uma porta lógica digital implementada com a tecnologia NMOS. Os transistores de chaveamento (com entradas vA e vB) são idênticos e do tipo enriquecimento, mas o transistor de carga é do tipo depleção. As tensões de limiar dos transistores de chaveamento e carga são 1 V e -3 V, respectivamente. Para esse circuito, o nível lógico alto (1 digital) é definido como qualquer tensão analógica compreendida entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com entrada em 5 V, a tensão de saída vO não excederá 0,3 V;

II somente com ambas as entradas simultaneamente no nível lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

Em condições estáticas, isto é, sem chaveamento dos níveis de entrada, a máxima dissipação de potência ocorre quando ambas as entradas estiverem fixadas em 5 V.

- C. Certo

- E. Errado

Engenharia Elétrica - Eletrônica digital - Centro de Seleção e de Promoção de Eventos UnB (CESPE) - 2010

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue os itens que se seguem.

- C. Certo

- E. Errado

Engenharia Elétrica - Iluminacao eletrica - Centro de Seleção e de Promoção de Eventos UnB (CESPE) - 2010

O proprietário de uma indústria solicitou a realização de um retrofit em todos os circuitos da instalação elétrica da indústria, visando com isso economizar energia. Além disso, a iluminação do pátio externo, que tem lâmpadas comandadas manualmente, deverá ter comando automático implementado com o uso de relés fotoelétricos.

Acerca dessa situação hipotética e dos fundamentos de projeto de instalações elétricas, julgue os itens subsequentes.

Caso as lâmpadas do pátio da indústria sejam de vapor de mercúrio, elas precisarão ser trocadas por lâmpadas incandescentes ou fluorescentes, uma vez que relés fotoelétricos não são adequados para comandar lâmpadas de vapor de mercúrio.

- C. Certo

- E. Errado