Questões sobre Eletrônica analógica e digital

Lista completa de Questões sobre Eletrônica analógica e digital para resolução totalmente grátis. Selecione os assuntos no filtro de questões e comece a resolver exercícios.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação Carlos Chagas (FCC) - 2006

Considere o circuito abaixo para responder às questões de números 52 e 53.

Sobre as características do amplificador operacional LM 741, é INCORRETO afirmar que

- A.

o ganho de tensão em malha aberta é elevado.

- B.

a largura de faixa é elevada.

- C.

amplifica sinais CC e CA.

- D.

a impedância de entrada é elevada.

- E.

a impedância de saída é elevada.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação Carlos Chagas (FCC) - 2006

Considere o circuito abaixo para responder às questões de números 52 e 53.

No circuito apresentado, se Ve = 1 Vpp, o valor de Vs será de, aproximadamente,

- A.

1 Vpp.

- B.

4,7 Vpp.

- C.

9,4 Vpp.

- D.

12 Vpp.

- E.

20 Vpp.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

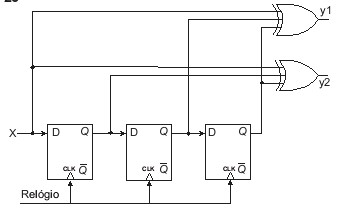

A figura acima ilustra o diagrama de um codificador convolucional de taxa ½, muito empregado na correção de erros em sistemas de transmissão digital. Nessa figura, X representa a seqüência binária gerada pela fonte e y1 e y2 são as seqüências codificadas. Admitindo-se que, inicialmente, os flip-flops armazenem o bit lógico 0 e que a seqüência de bits de entrada é X={1, 0, 1, 1}, as seqüências codificadas y1 e y2 são, respectivamente:

- A.

{1, 0, 1, 1} e {1, 0, 1, 1}

- B.

{1, 0, 1, 1} e {1, 1, 1, 1}

- C.

{1, 0, 1, 0} e {1, 0, 1, 1}

- D.

{1, 0, 0, 0} e {1, 1, 1, 1}

- E.

{1, 0, 0, 0} e {1, 0, 0, 0}

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

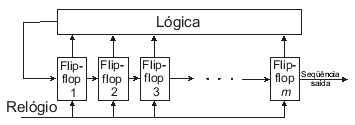

Observe abaixo o diagrama de blocos de um gerador de seqüências pseudo-aleatórias (PN).

Seqüências PN são empregadas em diversas aplicações, merecendo destaque o uso dessas seqüências na sincronização de receptores digitais e no espalhamento espectral de sistemas CDMA. O aumento da quantidade m de flipflops do registrador de deslocamento empregado no gerador permite que o(a):

- A.

pico de correlação de uma seqüência PN seja reduzido.

- B.

valor mínimo da correlação cruzada entre seqüências distintas aumente.

- C.

período da seqüência PN diminua.

- D.

número de 1s seja sempre igual ao de 0s.

- E.

quantidade de seqüências PN aumente.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

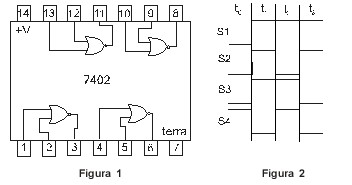

A Figura 1 acima representa um Circuito Integrado (CI) TTL 7402. Monta-se um circuito digital ligando-se o pino 6 ao pino 1 e o pino 2 ao pino 11 do CI. Considere que o CI esteja em perfeito estado e corretamente alimentado. Se as formas de onda S1, S2, S3 e S4 (Figura 2) forem aplicadas, respectivamente, nos pinos 4, 5, 12 e 13 do CI, a forma de onda produzida no pino 3 será representada por:

- A.

- B.

- C.

- D.

- E.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

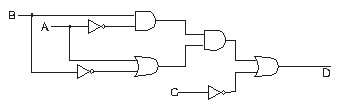

O circuito de lógica digital mostrado na figura acima pode ser simplificado para o circuito:

- A.

- B.

- C.

- D.

- E.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

A figura acima ilustra o diagrama de um codificador

convolucional de taxa ½, muito empregado na correção de

erros em sistemas de transmissão digital. Nessa figura,

Xrepresenta a seqüência binária gerada pela fonte e

y1 e y2são as seqüências codificadas. Admitindo-se que, inicialmente,

os

flip-flops armazenem o bit lógico 0 e que a seqüênciade bits de entrada é

X={1, 0, 1, 1}, as seqüências codificadasy1

e y2 são, respectivamente:- A.

{1, 0, 1, 1} e {1, 0, 1, 1}

- B.

{1, 0, 1, 1} e {1, 1, 1, 1}

- C.

{1, 0, 1, 0} e {1, 0, 1, 1}

- D.

{1, 0, 0, 0} e {1, 1, 1, 1}

- E.

{1, 0, 0, 0} e {1, 0, 0, 0}

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

Observe abaixo o diagrama de blocos de um gerador de seqüências pseudo-aleatórias (PN). Seqüências PN são empregadas em diversas aplicações, merecendo destaque o uso dessas seqüências na sincronização de receptores digitais e no espalhamento espectral de sistemas CDMA. O aumento da quantidade m de flipflops do registrador de deslocamento empregado no gerador permite que o(a):

- A.

pico de correlação de uma seqüência PN seja reduzido.

- B.

valor mínimo da correlação cruzada entre seqüências distintas aumente.

- C.

período da seqüência PN diminua.

- D.

número de 1's seja sempre igual ao de 0's.

- E.

quantidade de seqüências PN aumente.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

A Figura 1 acima representa um Circuito Integrado (CI) TTL 7402. Monta-se um circuito digital ligando-se o pino 6 ao pino 1 e o pino 2 ao pino 11 do CI. Considere que o CI esteja em perfeito estado e corretamente alimentado. Se as formas de onda S1, S2, S3 e S4 (Figura 2) forem aplicadas, respectivamente, nos pinos 4, 5, 12 e 13 do CI, a forma de onda produzida no pino 3 será representada por:

- A.

- B.

- C.

- D.

- E.

Engenharia de Telecomunicações - Eletrônica analógica e digital - Fundação CESGRANRIO (CESGRANRIO) - 2006

O circuito de lógica digital mostrado na figura acima pode ser simplificado para o circuito:

- A.

- B.

- C.

- D.

- E.